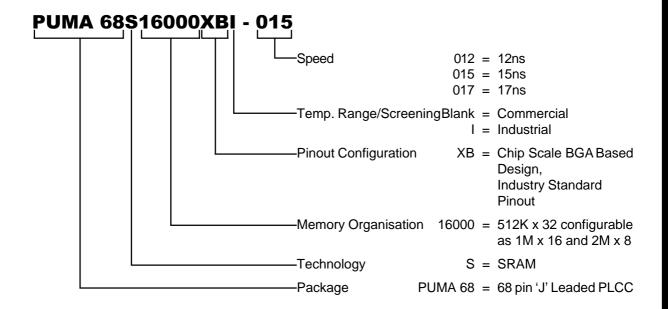

## PUMA 68S16000XB - 012/015/017

**Issue 5.2 March 2001**

#### **Description**

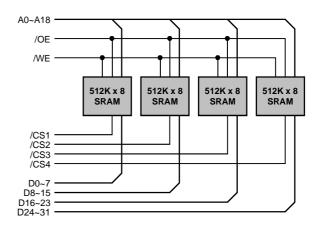

The PUMA68 range of devices provide a high density surface mount industry standard memory solution which may accommodate various memory technologies including SRAM, EEPROM and FLASH. The devices are designed to offer a defined upgrade path and may be user configured as 8, 16 or 32 bits wide.

The PUMA68S16000XB is a 512Kx32 SRAM module housed in a 68 'J' leaded package which complies with the JEDEC 68 PLCC standard. Access times of 12, 15 or 17ns are available.

The 5V device is available to commercial and industrial temperature grade.

#### **Block Diagram**

#### **Features**

- Access times of 12/15/17 ns.

- •5V + 10%.

- Comercial and Industrial temperature grades

- JEDEC standard 68 J Lead footprint.

- Industry standard pinout.

- May be organised as 512K x 32, 1M x 16, 2M X 8

- Operating Power (32 Bit) 4.18W (max)

- Low power standby. (TTL) 1.32W (max)

(CMOS) 220mW (max)

- Completely Static Operation.

# Pin Definition See page 2.

#### **Pin Functions**

| Description       | Signal          |

|-------------------|-----------------|

| Address Input     | A0~A18          |

| Data Input/Output | D0~D31          |

| Chip Select       | /CS1~4          |

| Write Enable      | /WE             |

| Output Enable     | /OE             |

| No Connect        | NC              |

| Power             | V <sub>cc</sub> |

| Ground            | $V_{SS}$        |

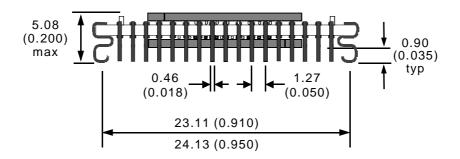

### **Package Details**

PUMA 68 - Plastic 68 'J' Leaded Package Max. Dimensions-25.27mm x 25.27mm x 5.08mm

## Pin Definition - PUMA68S16000XB

| Pin | Signal   | Pin | Signal   |

|-----|----------|-----|----------|

| 1   | $V_{CC}$ | 35  | $V_{CC}$ |

| 2   | NC       | 36  | A13      |

| 3   | /CS1     | 37  | A12      |

| 4   | /CS2     | 38  | A11      |

| 5   | /CS3     | 39  | A10      |

| 6   | /CS4     | 40  | A9       |

| 7   | A17      | 41  | A8       |

| 8   | A18      | 42  | A7       |

| 9   | D16      | 43  | D0       |

| 10  | D17      | 44  | D1       |

| 11  | D18      | 45  | D2       |

| 12  | D19      | 46  | D3       |

| 13  | $V_{SS}$ | 47  | $V_{SS}$ |

| 14  | D20      | 48  | D4       |

| 15  | D21      | 49  | D5       |

| 16  | D22      | 50  | D6       |

| 17  | D23      | 51  | D7       |

| 18  | $V_{CC}$ | 52  | $V_{CC}$ |

| 19  | D24      | 53  | D8       |

| 20  | D25      | 54  | D9       |

| 21  | D26      | 55  | D10      |

| 22  | D27      | 56  | D11      |

| 23  | $V_{SS}$ | 57  | $V_{SS}$ |

| 24  | D28      | 58  | D12      |

| 25  | D29      | 59  | D13      |

| 26  | D30      | 60  | D14      |

| 27  | D31      | 61  | D15      |

| 28  | A6       | 62  | A14      |

| 29  | A5       | 63  | A15      |

| 30  | A4       | 64  | A16      |

| 31  | А3       | 65  | /WE      |

| 32  | A2       | 66  | /OE      |

| 33  | A1       | 67  | NC       |

| 34  | A0       | 68  | NC       |

PAGE 2 Issue 5.2 March 2001

## Absolute Maximum Ratings(1)

| Parameter                                      | Symbol           | Min  |     | Max  | Unit |

|------------------------------------------------|------------------|------|-----|------|------|

| Voltage on any pin relative to V <sub>SS</sub> | V <sub>T</sub>   | -0.3 | to  | +6.0 | ٧    |

| Power Dissipation                              | P <sub>T</sub>   |      | 4.0 |      | W    |

| Storage Temperature                            | T <sub>STG</sub> | -55  | to  | +125 | °C   |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

## **Recommended Operating Conditions**

| Parameter             | Symbol                         | Min  | Тур | Max                  | Unit |            |

|-----------------------|--------------------------------|------|-----|----------------------|------|------------|

| Supply Voltage        | Vcc                            | 4.5  | 5.0 | 5.5                  | ٧    |            |

| Input High Voltage    | V <sub>IH</sub>                | 2.2  | -   | V <sub>CC</sub> +0.5 | V    |            |

| Input Low Voltage     | V <sub>IL</sub> <sup>(1)</sup> | -0.3 | -   | 0.8                  | V    |            |

| Operating Temperature | T <sub>A</sub>                 | 0    | -   | 70                   | оС   |            |

|                       | T <sub>AI</sub>                | -40  | -   | 85                   | оС   | (I Suffix) |

Notes: (1) Pulse Width: -2.0V for less than 10ns.

#### **DC Electrical Characteristics**

$(V_{CC} = 5V \pm 10\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter                             |        | Symbol            | Test Condition                                                                  | Min | Тур | Max | Unit |

|---------------------------------------|--------|-------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| Input Leakage Current                 |        | ILI               | V <sub>IN</sub> =0V to V <sub>CC</sub>                                          | -8  | 1   | 8   | μА   |

| Output Leakage Current                |        | I <sub>LO</sub>   | V <sub>I/O</sub> =0V to V <sub>CC</sub>                                         | -8  | -   | 8   | μA   |

| Average Supply Current <sup>(2)</sup> | 32 Bit | I <sub>CC32</sub> | $/CS^{(1)}=V_{IL}, I_{I/O}=0mA, f=f_{max}$                                      | -   | -   | 760 | mA   |

|                                       | 16 Bit | I <sub>CC16</sub> | As Above.                                                                       | -   | -   | 490 | mA   |

|                                       | 8 Bit  | I <sub>CC8</sub>  | As Above.                                                                       | -   | -   | 370 | mA   |

| Standby Supply Current                | TTL    | I <sub>SB</sub>   | /CS <sup>(1)</sup> =V <sub>IH</sub> ,Min Cycle                                  | -   | -   | 240 | mA   |

|                                       | CMOS   | I <sub>SB1</sub>  | /CS≥V <sub>CC</sub> -0.2V, 0.2V<br>≥V <sub>IN</sub> ≥V <sub>CC</sub> -0.2V, f=0 | -   | -   | 40  | mA   |

| Output Voltage Low                    |        | V <sub>OL</sub>   | I <sub>OL</sub> =8.0mA, V <sub>CC</sub> =Min                                    | -   | -   | 0.4 | V    |

| Output Voltage High                   |        | V <sub>OH</sub>   | I <sub>OH</sub> =-4.0mA, V <sub>CC</sub> =Min                                   | 2.4 | -   | -   | V    |

Notes (1) /CS1~4 inputs operate simultaneously for 32 bit mode, in pairs for 16 bit mode and singly for 8 bit mode.

(2) At  $f=f_{MAX}$  address and data inputs are cycling at max frequency.

PAGE 3 Issue 5.2 March 2001

## Capacitance

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, F=1MHz.)$

| Parameter                                   | Symbol           | Test Condition       | Min | Тур | Max | Unit |

|---------------------------------------------|------------------|----------------------|-----|-----|-----|------|

| Input Capacitance, Address, /OE, /WE        | C <sub>IN1</sub> | V <sub>IN</sub> =0V  | -   | -   | 30  | pF   |

| Output Capacitance, 8 bit mode (worst case) | C <sub>I/O</sub> | V <sub>I/O</sub> =0V | -   | -   | 34  | pF   |

Note: These Parameters are calculated not measured.

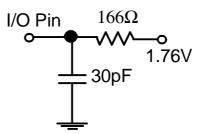

### **Test Conditions**

Input pulse levels : 0V to 3.0VInput rise and fall times : 3ns

• Input and Output timing reference levels: 1.5V

• Output Load : See Load Diagram.

•  $V_{CC} = 5V \pm 10\%$

• PUMA module tested in 32 bit mode.

## **Output Load**

## **Operation Truth Table**

| /CS1 | /CS2 | /CS3 | /CS4 | /OE | /WE | Supply Current                                         | Mode           |

|------|------|------|------|-----|-----|--------------------------------------------------------|----------------|

| L    | Н    | Η    | Η    | Χ   | ┙   | I <sub>CC8</sub>                                       | Write D0~D7    |

| Н    | L    | Η    | Η    | Χ   | L   | I <sub>CC8</sub>                                       | Write D8~D15   |

| Н    | Н    | Ш    | Η    | Χ   | ┙   | I <sub>CC8</sub>                                       | Write D16~D23  |

| Н    | Н    | Н    | L    | Χ   | L   | I <sub>CC8</sub>                                       | Write D24~D31  |

| L    | L    | Н    | Н    | Χ   | L   | I <sub>CC16</sub>                                      | Write D0~D15   |

| Н    | Н    | L    | L    | Χ   | L   | I <sub>CC16</sub>                                      | Write D16~D31  |

| L    | L    | L    | L    | Χ   | L   | I <sub>CC32</sub>                                      | Write D0~D31   |

| L    | Н    | Н    | Н    | L   | Η   | I <sub>CC8</sub>                                       | Read D0~D7     |

| Н    | L    | Н    | Н    | L   | Η   | I <sub>CC8</sub>                                       | Read D8~D15    |

| Н    | Н    | L    | Н    | Ш   | Η   | I <sub>CC8</sub>                                       | Read D16~D23   |

| Н    | Н    | Н    | L    | L   | Н   | I <sub>CC8</sub>                                       | Read D24~D31   |

| L    | L    | Н    | Н    | L   | Н   | I <sub>CC16</sub>                                      | Read D0~D15    |

| Н    | Н    | L    | L    | L   | Н   | I <sub>CC16</sub>                                      | Read D16~D31   |

| L    | L    | L    | L    | L   | Η   | I <sub>CC32</sub>                                      | Read D0~D31    |

| Х    | Х    | Х    | Х    | Η   | Η   | I <sub>CC32</sub> /I <sub>CC16</sub> /I <sub>CC8</sub> | D0~D31 High-Z  |

| Н    | Н    | Н    | Н    | Х   | Х   | I <sub>SB</sub> , I <sub>SB1</sub>                     | D0~D31 Standby |

Notes :  $H=V_{IH}$  :  $L=VI_L$  :  $X=V_{IH}$  or  $V_{IL}$

PAGE 4 Issue 5.2 March 2001

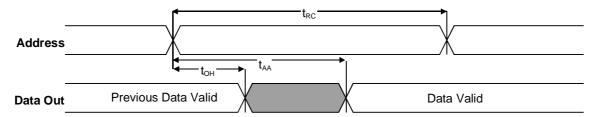

## Read Cycle

|                                      |                  | 12  |     | 15  |     | 17  |     |       |

|--------------------------------------|------------------|-----|-----|-----|-----|-----|-----|-------|

| Parameter                            | Symbol           | Min | Max | Min | Max | Min | Max | Units |

| Read Cycle Time                      | t <sub>RC</sub>  | 12  | 1   | 15  | -   | 17  | -   | ns    |

| Address Access Time                  | t <sub>AA</sub>  | -   | 12  | -   | 15  | -   | 17  | ns    |

| Chip Select Access Time              | t <sub>ACS</sub> | -   | 12  | -   | 15  | -   | 17  | ns    |

| Output Enable to Output Valid        | t <sub>OE</sub>  | -   | 6   | -   | 7   | -   | 8   | ns    |

| Output Hold From Address Change      | tон              | 3   | -   | 3   | -   | 3   | -   | ns    |

| Chip Selection to Output in Low Z    | t <sub>CLZ</sub> | 3   | -   | 3   | -   | 3   | -   | ns    |

| Output Enable to Output in Low Z     | t <sub>OLZ</sub> | 0   | -   | 0   | -   | 0   | -   | ns    |

| Chip Deselection to Output in High Z | t <sub>CHZ</sub> | 0   | 6   | 0   | 7   | 0   | 8   | ns    |

| Output Disable to Output in High Z   | t <sub>OHZ</sub> | 0   | 6   | 0   | 7   | 0   | 8   | ns    |

## Write Cycle

|                                 |                  | 12  |     | 12 15 |     | 1   | 7   |       |

|---------------------------------|------------------|-----|-----|-------|-----|-----|-----|-------|

| Parameter                       | Symbol           | Min | Max | Min   | Max | Min | Max | Units |

| Write Cycle Time                | t <sub>WC</sub>  | 12  | -   | 15    | -   | 17  | -   | ns    |

| Chip Selection to End of Write  | t <sub>CW</sub>  | 8   | -   | 10    | -   | 12  | -   | ns    |

| Address Valid to End of Write   | t <sub>AW</sub>  | 8   | -   | 10    | -   | 12  | -   | ns    |

| Address Setup Time              | t <sub>AS</sub>  | 0   | -   | 0     | -   | 0   | -   | ns    |

| Write Pulse Width (/OE High)    | t <sub>WP1</sub> | 8   | -   | 10    | -   | 12  | -   | ns    |

| Write Pulse Width (/OE Low)     | t <sub>WP2</sub> | 12  | -   | 12    | -   | 13  | -   | ns    |

| Write Recovery Time             | t <sub>WR</sub>  | 0   | -   | 0     | -   | 0   | -   | ns    |

| Write to Output in High Z       | t <sub>WHZ</sub> | 0   | 6   | 0     | 7   | 0   | 8   | ns    |

| Data to Write Time Overlap      | $t_{DW}$         | 6   | -   | 7     | -   | 8   | -   | ns    |

| Data Hold time from Write Time  | t <sub>DH</sub>  | 0   | -   | 0     | -   | 0   | -   | ns    |

| Output Active from End of Write | t <sub>OW</sub>  | 3   | -   | 3     | -   | 3   | -   | ns    |

PAGE 5 Issue 5.2 March 2001

## Read Cycle 1

(Address Controlled,  $/CS=/OE=V_{IL}$ ,  $/WE=V_{IH}$ )

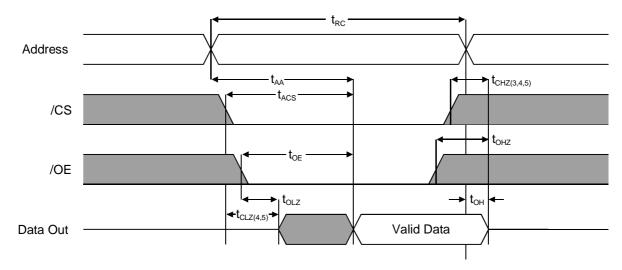

## Read Cycle 2

$$(/WE = V_{IH})$$

#### NOTES(READ CYCLE)

- 1. /WE is high for read cycle.

- All read cycle timing is referenced from the last valid address to the first transition address.

- t<sub>CHZ</sub> and t<sub>OHZ</sub> are defined as the time at which the outputs achieve the open circuit condition and are not referenced to V<sub>OH</sub> or V<sub>OL</sub> levels.

- At any given temperature and voltage condition, t CHZ(Max.) is less than t CLZ(Min.) both for a given device and from device to device.

- 5. Transition is measured ±200mV from steady state voltage with Load(B). This parameter is sampled and not 100% tested.

- 6. Device is continuously selected with /CS=V IL.

- 7. Address valid prior to coincident with /CS transition low.

- 8. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

9. /CS=/CS1~4

PAGE 6 Issue 5.2 March 2001

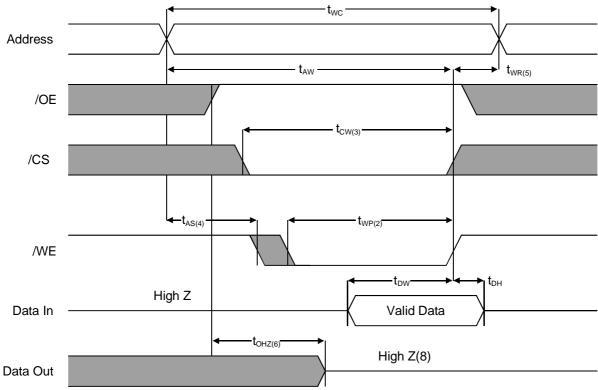

## Write Cycle 1

#### NOTES(WRITE CYCLE)

- 1. All write cycle timing is referenced from the last valid address to the first transition address.

- 2. A write occurs during the overlap of a low /CS and /WE. A write begins at the latest transition /CS going low and /WE going low; A write ends at the earliest transition /CS going high or /WE going high. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 3.  $t_{\text{CW}}$  is measured from the later of /CS going low to end of write.

- 4. t<sub>AS</sub> is measured from the address valid to the beginning of write.

- 5. t<sub>WR</sub> is measured from the end of write to the address change. t<sub>WR</sub> applied in case a write ends as /CS or /WE going high.

- 6. If OE, /CS and /WE are in the Read Mode during this period, the I/O pins are in the output low-Z state. Inputs of opposite phase of the output must not be applied because bus contention can occur.

- 7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

- 8. If /CS goes low simultaneously with /WE going or after /WE going low, the outputs remain high impedance state.

- 9. Dout is the read data of the new address.

- 10. When /CS is low: I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be applied.

11./CS=/CS1~4

PAGE 7 Issue 5.2 March 2001

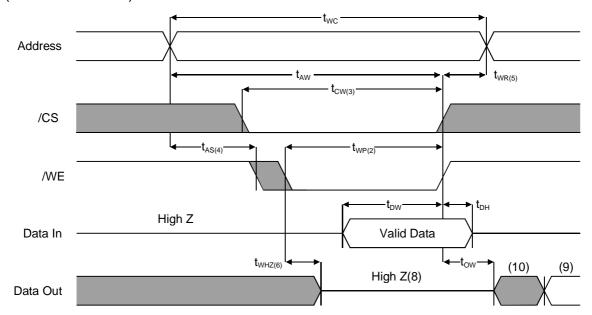

## Write Cycle 2

## (/OE = Low Fixed)

#### NOTES(WRITE CYCLE)

- 1. All write cycle timing is referenced from the last valid address to the first transition address.

- 2. A write occurs during the overlap of a low /CS and /WE. A write begins at the latest transition /CS going low and /WE going low; A write ends at the earliest transition /CS going high or /WE going high. twp is measured from the beginning of write to the end of write.

- 3.  $t_{\rm CW}$  is measured from the later of /CS going low to end of write. 4.  $t_{\rm AS}$  is measured from the address valid to the beginning of write.

- 5.  $t_{WR}$  is measured from the end of write to the address change.  $t_{WR}$  applied in case a write ends as /CS or /WE going high.

- 6. If OE, /CS and /WE are in the Read Mode during this period, the I/O pins are in the output low-Z state. Inputs of opposite phase of the output must not be applied because bus contention can occur.

- 7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

- 8. If /CS goes low simultaneously with /WE going or after /WE going low, the outputs remain high impedance state.

- 9. Dout is the read data of the new address.

- 10. When /CS is low: I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be applied.

11./CS=/CS1~4

Issue 5.2 March 2001 PAGE 8

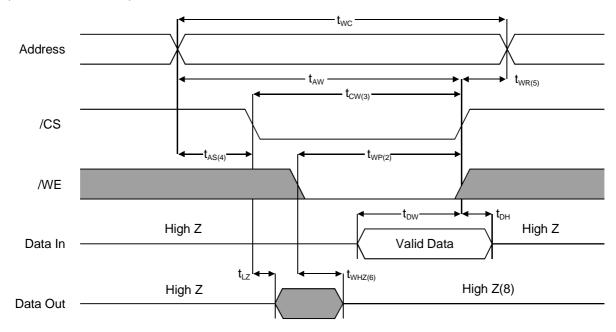

## **Write Cycle 3**

## (/CS = Controlled)

#### NOTES(WRITE CYCLE)

- 1. All write cycle timing is referenced from the last valid address to the first transition address.

- 2. A write occurs during the overlap of a low /CS and /WE. A write begins at the latest transition /CS going low and /WE going low;

A write ends at the earliest transition /CS going high or /WE going high. t we measured from the beginning of write to the end of write.

- 3.  $t_{\text{CW}}$  is measured from the later of /CS going low to end of write.

- 4. t<sub>AS</sub> is measured from the address valid to the beginning of write.

- 5. t<sub>WR</sub> is measured from the end of write to the address change. t <sub>WR</sub> applied in case a write ends as /CS or /WE going high.

- 6. If /OE, /CS and /WE are in the Read Mode during this period, the I/O pins are in the output low-Z state. Inputs of opposite phase of the output must not be applied because bus contention can occur.

- 7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

- 8. If /CS goes low simultaneously with /WE going or after /WE going low, the outputs remain high impedance state.

- 9. Dout is the read data of the new address.

- 10.When /CS is low: I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be applied.

11/CS=/CS1~4

PAGE 9 Issue 5.2 March 2001

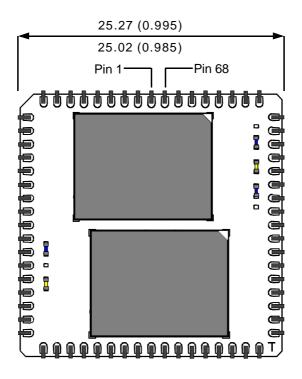

## **PUMA 68 Pin JEDEC Surface Mount PLCC**

Notes:

1. All dimensions in mm (inches).

PAGE 10 Issue 5.2 March 2001

## **Ordering Information**

#### Note:

Although this data is believed to be accurate the information contained herein is not intended to and does not create any warranty of merchantibility or fitness for a particular purpose.

Our products are subject to a constant process of development. Data may be changed without notice.

Products are not authorised for use as critical components in life support devices without the express written approval of a company director.

PAGE 11 Issue 5.2 March 2001

#### **Moisture Sensitivity**

Devices are moisture sensitive.

Shelf Life in Sealed Bag 12 months at <40°C and <90% relative humidity (RH).

After this bag has been opened, devices that will be subjected to infrared reflow, vapour phase reflow, or equivalent processing (peak package body temp 220°C) **must be**:

A: Mounted within 72 Hours at factory conditions of <30°C/60% RH

#### OR

B: Stored at <20% RH

If these conditions are not met or indicator card is >20% when read at  $23^{\circ}$ C +/-5% devices **require baking** as specified below.

If baking is required, devices may be baked for :-

A: 24 hours at 125°C +/-5% for high temperature device containers

#### OR

B: 192 hours at 40°C +5°C/-0°C and <5% RH for low temperature device containers.

#### **Packaging Standard**

Packaged in trays as standard.

Tape and reel available for shipment quantities exceeding 200pcs upon request.

#### **Soldering Recomendations**

IR/Convection - Ramp Rate 6°C/sec max.

Temp. exceeding 183°C 150 secs. max.

Peak Temperature 225°C

Time within 5°C of peak 20 secs max. Ramp down 6°C/sec max.

Vapour Phase - Ramp up rate 6°C/sec max.

Peak Temperature 215 - 219°C Time within 5°C of peak 60 secs max. Ramp down 6°C/sec max.

Note: The above recomendations are based on standard industry practice. Failiure to comply with the above recomendations invalidates product warranty.

PAGE 12 Issue 5.1 April 2000